**PLATAFORMA DIDÁTICA PARA DESENVOLVIMENTO DE ESTRATÉGIAS PWM

PARA CONVERSORES DE POTÊNCIA VIA DSP E FPGA - UMA ABORDAGEM

PARA DESENVOLVIMENTO**

Douglas de Souza Almeida <sup>1</sup>, Maurício Beltrão de Rossiter Corrêa <sup>2</sup>

**RESUMO**

Este relatório aborda o desenvolvimento de estratégias PWM (Pulse Width Modulation) para conversores de potência, destacando o uso de DSP (Digital Signal Processing) e FPGA (Field-Programmable Gate Array) como ferramentas essenciais para o controle de sistemas de energia eficientes. As estratégias PWM são cruciais para regular a energia em sistemas de potência, e o DSP permite a implementação de algoritmos de controle complexos. Na primeira fase do projeto, concentrou-se na compreensão das técnicas PWM seno-triângulo e PWM vetorial. Também foi iniciado o estudo de conversores multiníveis e o uso de FPGA para controle. Na segunda fase, um inversor NPC de 3 níveis foi controlado usando um DSP, com geração precisa de sinais PWM e filtragem. A eficiência do DSP foi destacada pelo tempo de cálculo curto. As simulações foram validadas com medições reais.

**Palavras-chave:** DSP, FPGA, conversores multiníveis.

---

<sup>1</sup> Aluno de Engenharia Elétrica, UAEE, UFCG, Campina Grande, PB, e-mail: douglas.almeida@ee.ufcg.edu.br

<sup>2</sup> Doutor, Professor, UAEE, UFCG, Campina Grande, PB, e-mail: mbrcorrea@dee.ufcg.edu.br

# ***EDUCATIONAL PLATFORM FOR PWM STRATEGY DEVELOPMENT FOR POWER CONVERTERS VIA DSP AND FPGA - AN APPROACH TO DEVELOPMENT***

## **ABSTRACT**

This report addresses the development of Pulse Width Modulation (PWM) strategies for power converters, emphasizing the use of Digital Signal Processing (DSP) and Field-Programmable Gate Arrays (FPGA) as essential tools for controlling efficient power systems. PWM strategies are crucial for regulating power in power systems, and DSP allows for the implementation of complex control algorithms. In the first phase of the project, the focus was on understanding sine-triangle PWM and space vector PWM techniques. Additionally, the study of multilevel converters and the use of FPGA for control were initiated. In the second phase, a 3-level NPC inverter was controlled using a DSP, with precise PWM signal generation and filtering. The efficiency of the DSP was highlighted by its short calculation time. Simulations were validated with real measurements.

**Keywords:** DSP, FPGA, multilevel converters.

## INTRODUÇÃO

O desenvolvimento de estratégias PWM (Pulse Width Modulation) para conversores de potência via DSP (Digital Signal Processing) e FPGA (Field-Programmable Gate Array) é uma área de pesquisa e desenvolvimento fundamental para sistemas de energia modernos e eficientes.

Os conversores de potência são dispositivos eletrônicos que convertem energia elétrica de uma forma para outra. Eles são amplamente utilizados em sistemas de energia renovável, controle de motores elétricos, eletrônica de potência e muitas outras aplicações.

De acordo com Grigoletto (2009), as estratégias PWM são essenciais para controlar a magnitude da tensão ou corrente de saída dos conversores de potência. Elas permitem que o sinal de saída seja modulado com uma frequência alta para controlar a quantidade de energia transferida do conversor para o sistema. Isso permite uma regulação precisa e eficiente da energia em sistemas de controle de potência.

Com o uso de DSP e FPGA, é possível implementar estratégias PWM complexas que garantem um melhor desempenho e eficiência do sistema de controle de potência. O DSP é capaz de processar sinais de alta frequência com precisão, enquanto o FPGA pode ser programado para executar algoritmos complexos em tempo real.

O desenvolvimento de estratégias PWM para conversores de potência via DSP e FPGA é uma área em constante evolução, com novas estratégias sendo desenvolvidas e aprimoradas continuamente. Com a crescente demanda por sistemas de energia mais eficientes e renováveis, esta área é fundamental para o avanço da eletrônica de potência e sistemas de controle de energia (SANTANA, 2006; CASTRO, 2013).

## MATERIAIS E MÉTODOS (OU METODOLOGIA)

Durante a primeira fase do projeto, os esforços foram concentrados na compreensão das técnicas de PWM seno-triângulo aplicadas a um conversor de fonte de tensão monofásico. Simulações foram realizadas usando os softwares Octave e PSIM.

A técnica de PWM seno-triângulo envolve a comparação de um sinal de referência senoidal com um sinal de referência triangular. O sinal senoidal controla a amplitude da saída do conversor, enquanto o sinal triangular controla a frequência. Essa técnica baseia-se na variação da largura de pulso dos sinais de comutação do conversor para manter a saída o mais próxima possível da forma de onda senoidal

de referência. A largura de pulso é controlada pela comparação entre o sinal senoidal e o sinal triangular.

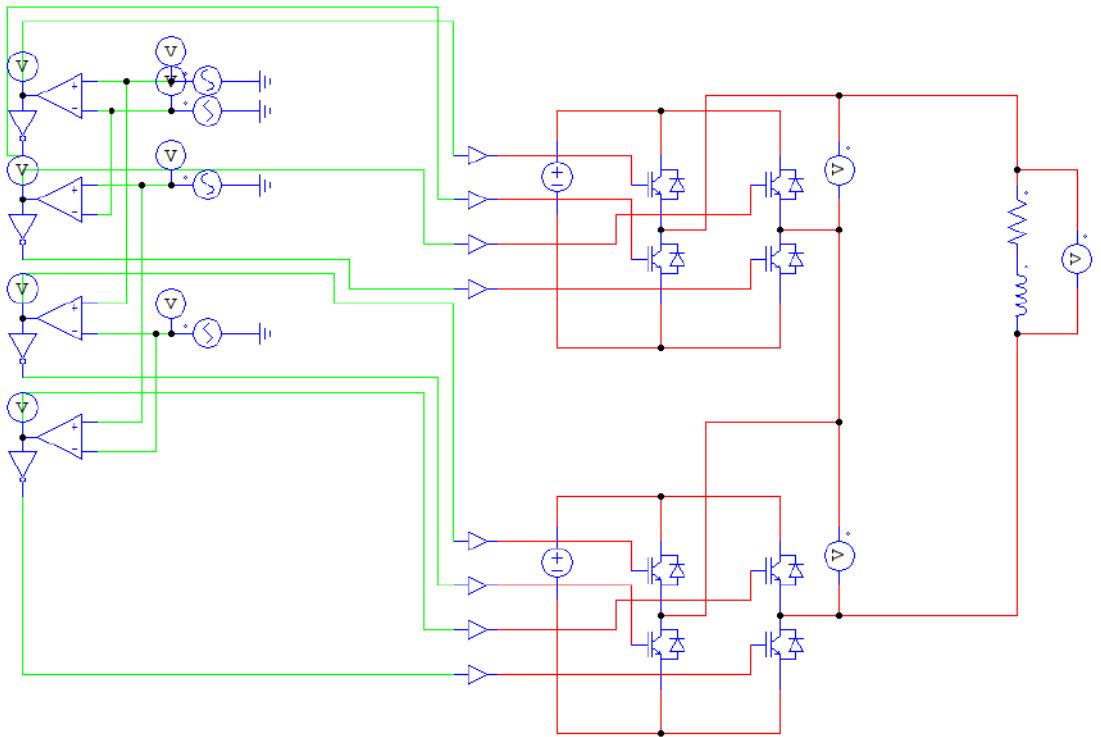

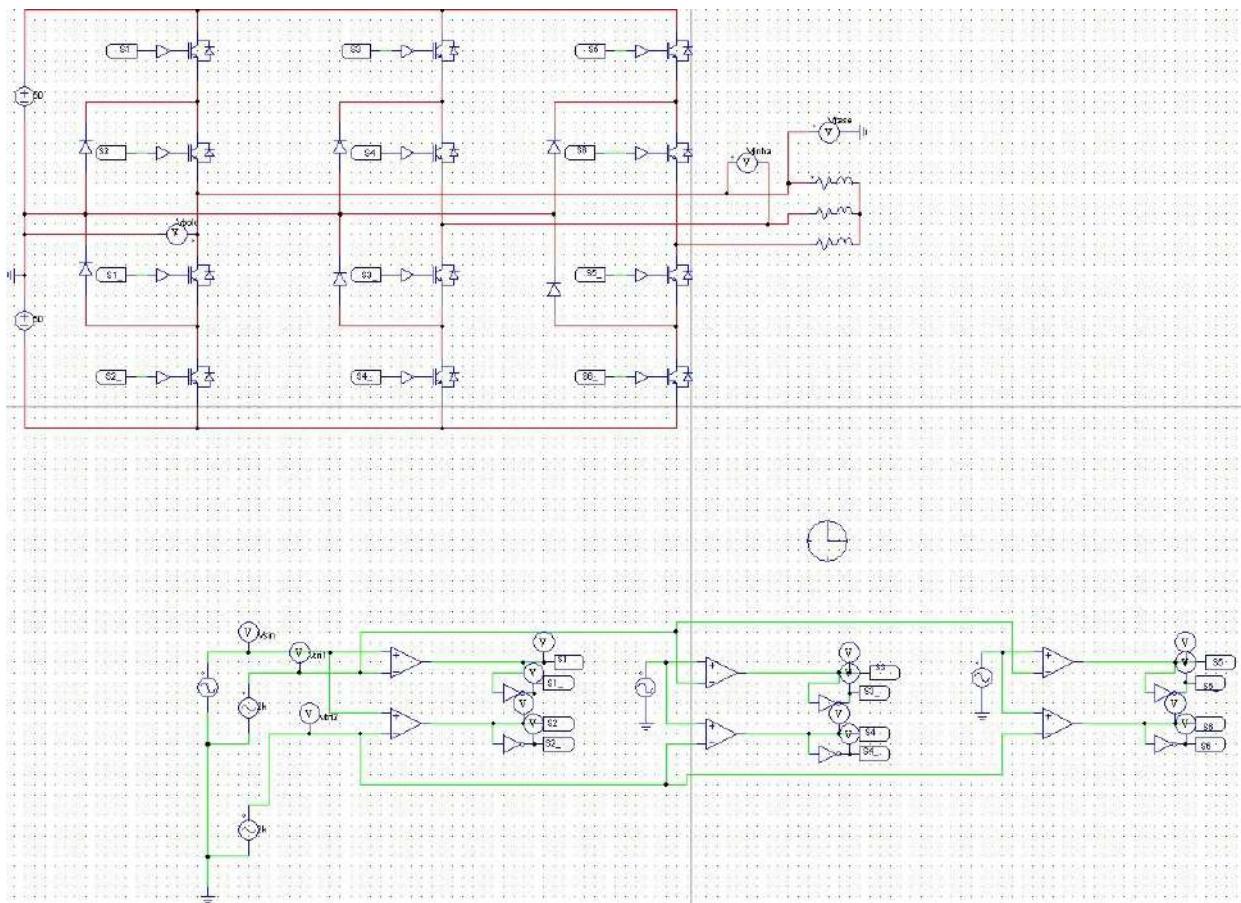

Fig. 1 - Circuito do inversor ponte H em cascata com duas células no PSIM.

FONTE: Próprio Autor.

Além disso, implementamos o PWM vetorial (figura 2), conhecido como SVPWM (Space Vector Pulse Width Modulation), em sistemas de eletrônica de potência. Ao contrário da técnica seno-triângulo, o SVPWM utiliza um espaço vetorial para gerar pulsos de saída. Esse espaço é formado por um conjunto de vetores que representam as combinações possíveis dos pulsos de saída do conversor.

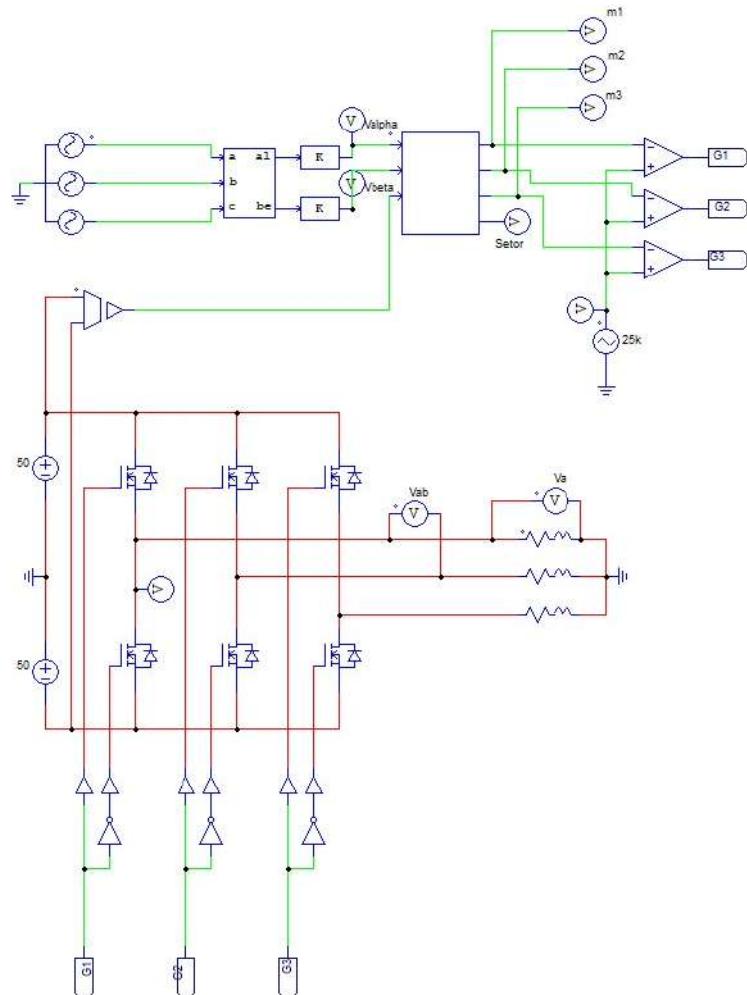

Fig. 2 - Circuito do inversor trifásico com PWM vetorial no PSIM.

FONTE: Próprio Autor.

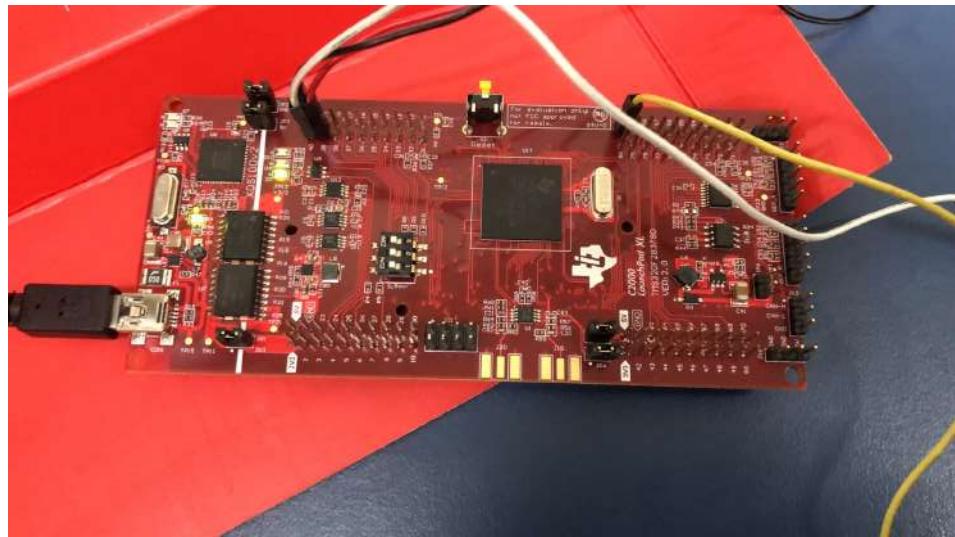

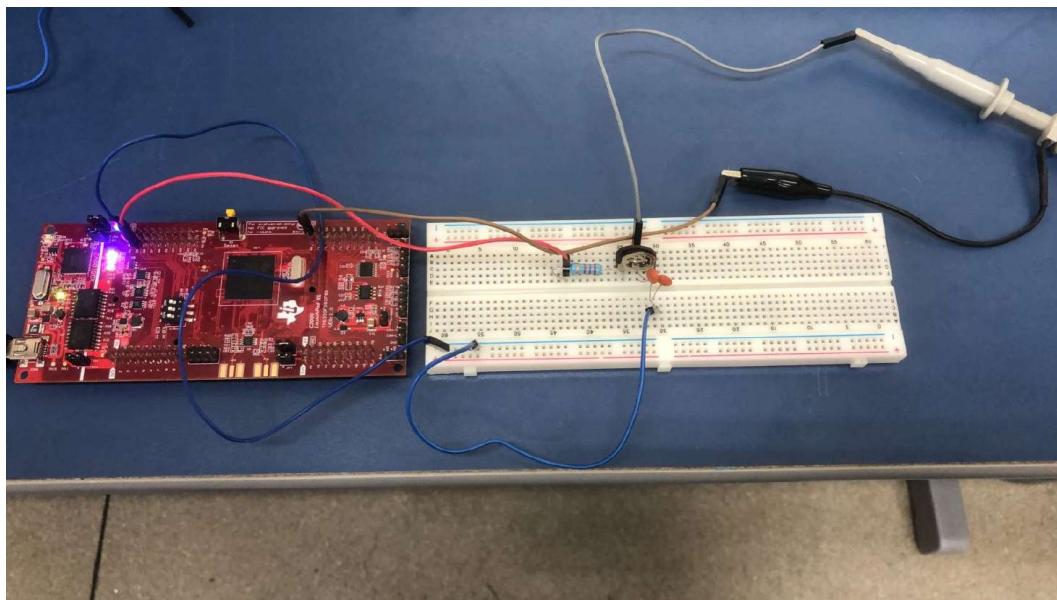

Na segunda etapa do projeto, conduzida no Laboratório de Eletrônica Industrial e Acionamento de Máquinas (LEIAM) da UFCG, foi iniciado a implementação de sinais de controle PWM para um conversor NPC (Neutral-Point Clamped) multinível de três níveis através do DSP (Digital Signal Processor).

Para alcançar esse objetivo, utilizamos vários equipamentos e materiais essenciais para a realização das atividades. O principal instrumento foi o DSP da Texas Instruments, modelo LAUNCHXL-F28379D. Além do DSP, usamos um osciloscópio para monitorização, análise e verificação dos sinais gerados. Isso nos permitiu avaliar o desempenho do sistema em relação às saídas desejadas.

Fig. 3 - DSP da Texas Instruments LAUNCHXL-F28379D.

FONTE: Próprio Autor.

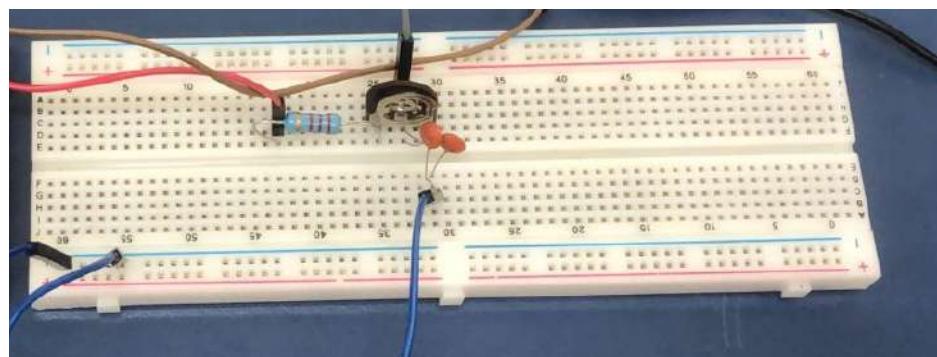

A implementação dos sinais de controle PWM também envolveu a montagem de um filtro RC, que condicionou os sinais gerados pelo DSP. O uso deste filtro foi utilizado como parte do processo de verificação dos sinais PWM gerados pelo DSP garantindo que os sinais estejam de acordo com as especificações.

Fig. 4 - Filtro RC.

FONTE: Próprio Autor.

## DESENVOLVIMENTO

Inicialmente os conversores multiníveis NPC e Cascata foram definidos como objetos de estudo. O inversor em cascata simétrico é composto pela conexão em série de dois ou mais conversores monofásicos em ponte completa com capacitores

isolados de mesma tensão (Vcc). Na prática, o número de células de potência nesse inversor é determinado principalmente por sua tensão de operação e custo de fabricação. O uso de células de potência idênticas leva a uma estrutura modular, que é um meio eficaz para a redução de custos (LACERDA FILHO, 2019).

Cada conversor monofásico pode ser interpretado como uma célula independente, contendo quatro dispositivos semicondutores, quatro diodos em antiparalelo e um capacitor. Cada célula pode produzir tensões com três níveis de saída: 0, -Vcc e +Vcc. A tensão de saída do conversor vista pelos terminais a e n é definida pela soma das saídas de cada célula (KATHAR E KULKARNI, 2017).

**Tabela 1. Tensões de entrada e saída dos inversores multiníveis**

| Inversor            | Tensão de Entrada (V) | Níveis da Tensão de Saída (V)                                                |

|---------------------|-----------------------|------------------------------------------------------------------------------|

| Cascata Ponte H     | Vcc                   | $+Vcc$ , $\frac{+Vcc}{2}$ , 0, $\frac{-Vcc}{2}$ , $-Vcc$                     |

| NPC                 | Vcc                   | $\frac{+Vcc}{2}$ , $\frac{+Vcc}{4}$ , 0, $\frac{-Vcc}{4}$ , $\frac{-Vcc}{2}$ |

| Capacitor Flutuante | Vcc                   | $\frac{+Vcc}{2}$ , $\frac{+Vcc}{4}$ , 0, $\frac{-Vcc}{4}$ , $\frac{-Vcc}{2}$ |

FONTE: Próprio Autor.

**Tabela 2. Número de Componentes do Conversor Multinível em Cascata Simétrico**

| Nível de Tensão | Chaves Ativas | Diodos | Capacitores barramento CC | Capacitores de grampeamento |

|-----------------|---------------|--------|---------------------------|-----------------------------|

| m               | 6(m-1)        | 0      | 1.5(m-1)                  | 0                           |

| 3               | 12            | 0      | 3                         | 0                           |

| 5               | 24            | 0      | 6                         | 0                           |

FONTE: Próprio Autor.

No inversor multinível NPC a tensão CC do barramento (Vcc) é dividida em três níveis que são:  $+Vcc/2$ , 0 e  $-Vcc/2$ , sendo que, para isso, existem dois capacitores em série paralelos ao barramento. Cada célula de comutação também apresenta um par de transistores ou tiristores superiores, um par de transistores ou tiristores inferiores. O

número de células depende do número de níveis de tensão desejados na saída e a tensão máxima entre os terminais a-n para quaisquer n níveis é  $V_{cc}/2$ .

É baseado na combinação adequada dos dispositivos semicondutores nas células de comutação. Ao alternar as chaves de comutação, os níveis de tensão nos capacitores de ponto neutro são ajustados, permitindo a geração de uma forma de onda de tensão multinível na saída.

**Tabela 3. Número de Componentes do Conversor Multinível NPC**

| Nível de Tensão | Chaves Ativas | Diodos        | Capacitores barramento CC | Capacitores de grampeamento |

|-----------------|---------------|---------------|---------------------------|-----------------------------|

| m               | $6(m-1)$      | $3(m-1)(m-2)$ | $(m-1)$                   | 0                           |

| 3               | 12            | 6             | 2                         | 0                           |

| 5               | 24            | 36            | 4                         | 0                           |

FONTE: Próprio Autor.

Para realizar o controle das chaves semicondutoras nos projetos dos conversores multiníveis podem ser utilizados o DSP (Digital Signal Processor), o FPGA ou microcontroladores.

O DSP é um dispositivo programável e possui seu próprio código de instrução, ou seja, cada empresa que cria seu processador também cria seu próprio ambiente de desenvolvimento. A tecnologia DSP possui arquitetura otimizada para computação intensiva estando presente em dispositivos como celulares, computadores multimídia, gravadores de vídeos, modems, etc.

O DSP pode executar operações matemáticas complexas, como multiplicação de números de ponto flutuante, filtragem digital e transformada rápida de Fourier (FFT), para realizar esses cálculos de controle de forma eficiente. Entretanto, os DSPs apresentam menor flexibilidade que os FPGAs em termos de modificações de hardware para se adequar a novas funcionalidades.

O FPGA é um dispositivo semicondutor constituído de unidades lógicas (na ordem de milhares) em um único circuito integrado (CI), cujas interconexões podem ser programadas pelo usuário, podendo reproduzir desde lógicas simples (como funções AND, OR, NOT), até sistemas combinacionais mais complexos, o que acrescenta enorme flexibilidade ao projeto. Essa característica é uma das principais vantagens de se utilizar os FPGAs, além de diminuir custos de desenvolvimento.

Portanto, o DSP é usado principalmente para realizar cálculos complexos e controle de malha fechada em inversores de frequência, enquanto o FPGA é usado para implementar a lógica digital que controla o fluxo de energia e oferece maior flexibilidade de projeto (PIMENTEL, 2006).

## RESULTADOS E DISCUSSÕES

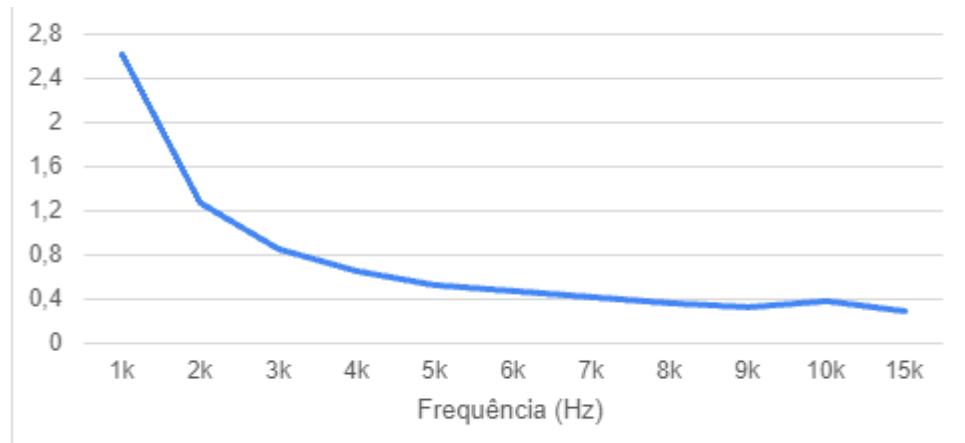

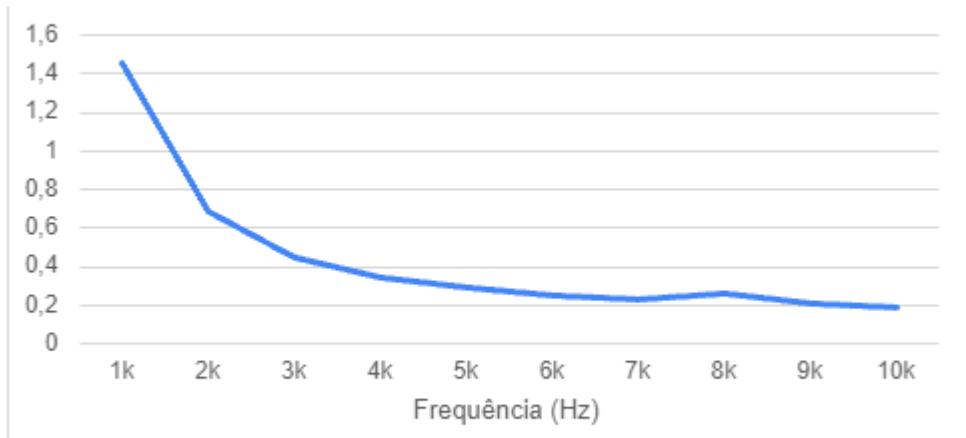

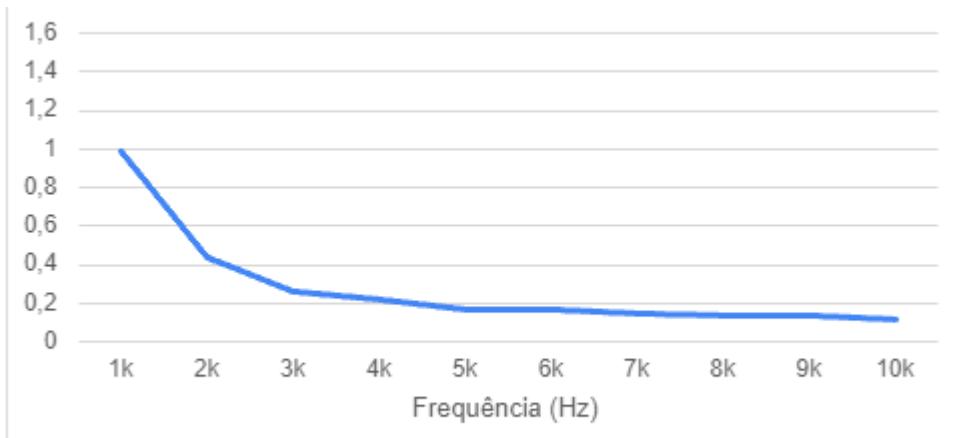

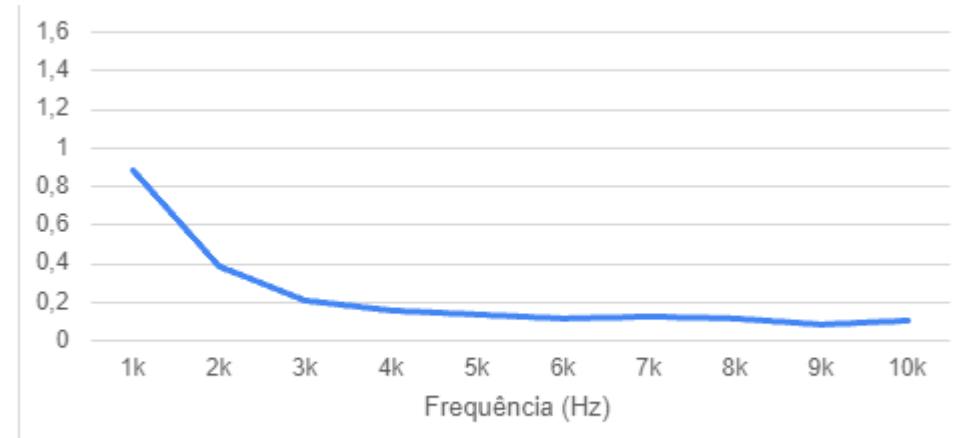

Com base nos dados obtidos nas simulações realizadas no PSIM para inversores NPC de 3, 4 e 5 níveis, geramos três gráficos para analisar a variação do wTHD (*Weighted Total Harmonic Distortion* - Distorção Harmônica Total ponderada) à medida que a frequência de chaveamento foi alterada. Foi empregado um índice de modulação de 0,9 e apenas o inversor trifásico de 2 níveis foi simulado utilizando a técnica de modulação SVPWM, enquanto os demais foram simulados com a técnica Level Shifted.

Fig. 5 - Variação do wTHD em Função da Frequência de Chaveamento para Inversor Trifásico de 2 níveis

FONTE: Próprio Autor.

Fig. 6 - Variação do wTHD em Função da Frequência de Chaveamento para Inversor NPC de 3 níveis

FONTE: Próprio Autor.

Fig. 7 - Variação do wTHD em Função da Frequência de Chaveamento para Inversor NPC de 4 níveis

FONTE: Próprio Autor.

Fig. 8 - Variação do wTHD em Função da Frequência de Chaveamento para Inversor NPC de 5 níveis

FONTE: Próprio Autor.

Ao comparar os valores de wTHD para os inversores NPC de 3, 4 e 5 níveis, observamos uma tendência geral de redução do wTHD à medida que a frequência aumenta em todas as configurações. Isso indica que todos os inversores tendem a apresentar menor distorção harmônica em frequências mais altas.

Para todas as configurações dos inversores NPC, podemos observar que o wTHD diminui à medida que a frequência aumenta. Essa tendência sugere que a atenuação da distorção harmônica é mais eficaz em frequências mais altas, independentemente do número de níveis do inveror.

O inveror NPC de 5 níveis apresenta, em geral, os valores mais baixos de wTHD em comparação com os inversores de 3 e 4 níveis. Isso sugere que a adição de mais níveis no inveror NPC pode contribuir para uma menor distorção harmônica em diferentes frequências.

Observa-se que o inveror NPC com modulação Level Shifted demonstrou uma eficiência superior em relação ao wTHD quando comparado ao inveror trifásico convencional de dois níveis com modulação SVPWM. Essa diferença fica evidente ao analisar os gráficos, onde pode-se observar que, por exemplo, o inveror de dois níveis com uma frequência de 10 kHz possui um wTHD de 0,3846%, enquanto o inveror NPC de 5 níveis atinge esse mesmo valor com apenas 2 kHz de frequência.

Esses resultados indicam que o inveror NPC com modulação Level Shifted é capaz de fornecer uma qualidade de forma de onda de saída superior, com menor distorção harmônica, em frequências mais baixas. Isso é especialmente notável ao compará-lo com o inveror de dois níveis com modulação SVPWM, que exige uma frequência mais alta para alcançar um wTHD semelhante.

Essa diferença de eficiência entre as duas técnicas de modulação pode ser atribuída à capacidade do inveror NPC de controlar de forma mais precisa os harmônicos de baixa frequência. A modulação Level Shifted proporciona uma melhor atenuação desses harmônicos, resultando em um menor wTHD em frequências mais baixas.

Com base na análise comparativa realizada, é recomendado o uso de inveror NPC de 5 níveis, uma vez que ele apresenta, em geral, menor wTHD em comparação com os inversores de 3 e 4 níveis e também com o trifásico de 2 níveis. No entanto, é importante considerar outros fatores, como custo, complexidade e eficiência, ao selecionar a configuração adequada do inveror NPC para uma aplicação específica.

Um exemplo de norma que aborda o THD é a norma IEEE 519, que define limites para a distorção harmônica em sistemas elétricos de potência. Essa norma

estabelece limites específicos para a distorção harmônica total de tensão e corrente em diferentes pontos do sistema elétrico, levando em consideração as características e requisitos dos equipamentos conectados (IEEE Std 519-1992).

**Tabela 4. Vantagens e Desvantagens dos inversores multiníveis**

|              | Inversores Cascata em Ponte H                                                                                                                                                         | Inversores NPC                                                                                                                                                             | Inversores com Capacitor Flutuante                                                                                                                                                                         |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vantagens    | <ul style="list-style-type: none"> <li>• Obtemos a mesma frequência de chaveamento para todos chaveamentos;</li> <li>• Estrutura modular, portanto mais fácil de analisar.</li> </ul> | <ul style="list-style-type: none"> <li>• Baixo custo e menos componentes devido ao menor número de capacitores;</li> <li>• Melhor qualidade de energia.</li> </ul>         | <ul style="list-style-type: none"> <li>• Cada célula pode ser analisada separadamente;</li> <li>• Redução do número de componentes.</li> </ul>                                                             |

| Desvantagens | <ul style="list-style-type: none"> <li>• Necessário fontes CC separadas;</li> <li>• Tensões desbalanceadas;</li> <li>• Maior número de dispositivos de potência.</li> </ul>           | <ul style="list-style-type: none"> <li>• Complexidade no controle;</li> <li>• Necessário vários diodos;</li> <li>• Maior estresse nos dispositivos de potência.</li> </ul> | <ul style="list-style-type: none"> <li>• Requer um capacitor de alta tensão;</li> <li>• Necessidade de controle do capacitor flutuante;</li> <li>• Custo adicional do capacitor de alta tensão.</li> </ul> |

FONTE: Próprio Autor.

Fig. 9 - Inversor NPC de 3 níveis simulado no PSIM

FONTE: Próprio Autor.

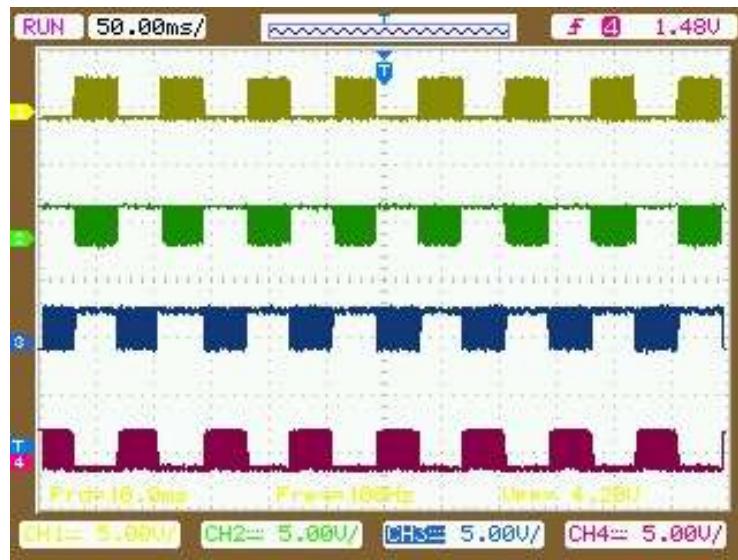

Na segunda fase do projeto, foi iniciado a implementação prática do controle de um inversor NPC de 3 níveis usando um DSP. Geramos sinais de controle PWM para as fases A, B e C do inversor NPC. Isso incluiu a definição da frequência de chaveamento, que foi definida em 18kHz, e a escolha da técnica de modulação, que no nosso caso foi a Modulação por Largura de Pulso Senoidal (SPWM). A Figura 10 mostra os sinais de controle gerados para a fase A, as demais fases são semelhantes, mudando apenas a defasagem. Podemos observar a modulação precisa que mantém a saída do inversor em conformidade com as formas de onda desejadas.

Fig. 10 - Saídas da Fase A no osciloscópio

FONTE: Próprio Autor.

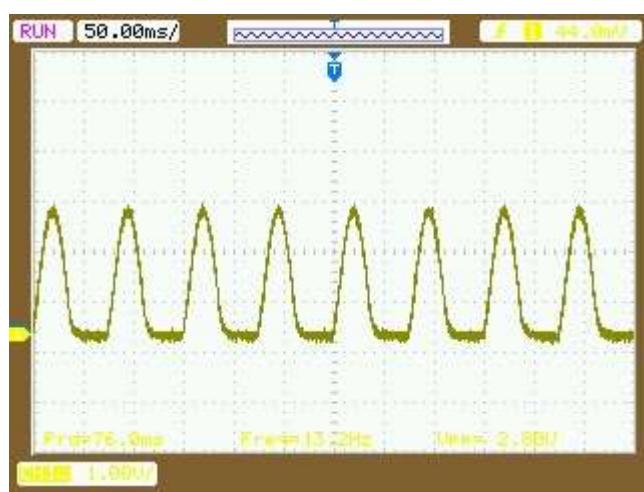

As saídas PWM geradas pelo DSP após passarem por um filtro RC, suavizou as saídas e reduziu componentes de alta frequência. A Figura 11 apresenta a forma de onda da saída PWM1A após esse processo de filtragem. Essa representação indica a eficácia da filtragem na produção de sinais suaves e controlados, como também para a verificação dos sinais PWM gerados pelo DSP garantindo que os sinais estejam de acordo com as especificações.

Fig. 11 - Saídas da Fase A no osciloscópio

FONTE: Próprio Autor.

Fig. 12 - Montagem do circuito

FONTE: Próprio Autor.

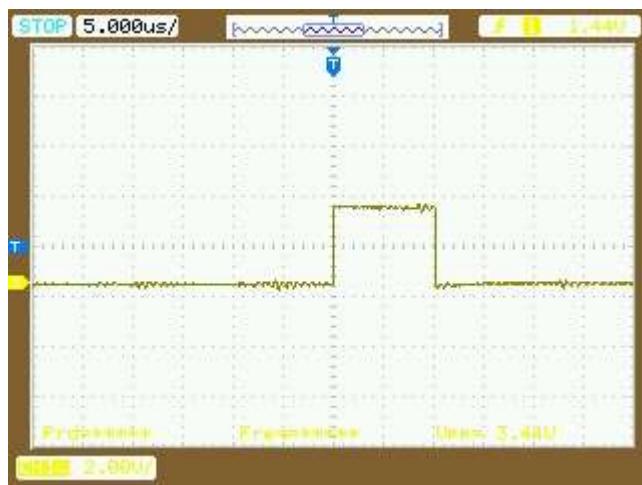

Fig. 13 - Tempo de cálculo por interrupção

FONTE: Próprio Autor.

Durante as medições e análises do sistema, também monitoramos o tempo de cálculo necessário pelo DSP a cada interrupção. Observamos que o DSP completou seus cálculos em um tempo médio de 10 microssegundos ( $10\mu\text{s}$ ) por interrupção. Isso é especialmente significativo em relação ao período de operação do sistema, que é de 55,55 microssegundos ( $55,55\mu\text{s}$ ). Essa eficiência no tempo de cálculo é um indicativo do desempenho satisfatório do DSP em nosso sistema de controle, tendo em vista que ele ainda suportaria uma grande parcela de tarefas adicionais.

Para validar nossos resultados, comparamos as saídas PWM simuladas no software PSIM com as medições realizadas no osciloscópio. Essa comparação nos

permitiu verificar a precisão de nosso modelo de simulação em relação à realidade. Embora tenhamos observado algumas diferenças, principalmente as características do hardware e imperfeições do filtro RC, as tendências gerais foram consistentes entre as simulações e as medições reais.

Nesta fase do projeto, alcançamos resultados significativos na implementação do controle do inversor NPC de 3 níveis. A comparação entre simulações e medições reais validou nossa abordagem e demonstrou sua aplicabilidade prática.

Fig. 14 - FPGA DE10-Lite

FONTE: Próprio Autor.

Podemos constatar também, que quando o número de níveis do inversor multinível excede a quantidade de saídas PWM disponíveis no DSP, a troca para uma FPGA pode ser considerada para obter a quantidade de saídas PWM necessárias. Em um FPGA, pode-se projetar a lógica digital específica para gerar a quantidade desejada de saídas PWM independentes, permitindo o controle de inversores multinível com um alto número de níveis. Isso proporciona uma maior flexibilidade na configuração do inversor e a capacidade de lidar com topologias multiníveis mais complexas.

No decorrer deste projeto, dedicamos esforços significativos à integração da FPGA em nossa pesquisa. Nossa intenção era utilizar a FPGA como uma parte fundamental da implementação de nossos conceitos teóricos em um ambiente prático. Para atingir esse objetivo, participamos de um curso de treinamento ministrado pela Macnica DHW, com o apoio do LEIAM, que nos proporcionou uma visão aprofundada das capacidades da FPGA e da ferramenta Quartus.

Durante o curso, exploramos conceitos essenciais relacionados à FPGA e à linguagem de descrição de hardware Verilog. Também tivemos a oportunidade de trabalhar diretamente com a placa de desenvolvimento da FPGA, conhecendo suas funcionalidades e capacidades. Embora tenhamos adquirido um conhecimento valioso, infelizmente, devido a restrições de tempo, não conseguimos implementar todas as funcionalidades planejadas na FPGA. No entanto, destaco que as limitações de tempo não comprometeram a qualidade ou os objetivos principais de nosso projeto. O curso teve uma duração total de 20 horas e incluiu o uso do kit ilustrado na Figura 14.

## CONCLUSÃO

Ao analisar os resultados apresentados, podemos concluir que a implementação do controle do inversor NPC de 3 níveis usando o DSP foi bem-sucedida em produzir saídas PWM controladas. Os sinais de controle e saídas PWM atenderam às especificações do projeto e demonstraram a eficácia da técnica de modulação SPWM para esse fim.

Identificamos desafios, como as discrepâncias entre as simulações e as medições reais, que nos levam a considerar melhorias futuras no sistema. Alcançamos resultados significativos na implementação do controle do inversor NPC de 3 níveis. A comparação entre simulações e medições reais validou nossa abordagem e demonstrou sua aplicabilidade prática.

Além disso, enfatizamos a importância de considerar a transição para uma FPGA quando o número de níveis do inversor multinível excede a quantidade de saídas PWM disponíveis no DSP. A FPGA oferece flexibilidade na configuração do inversor e a capacidade de lidar com topologias multiníveis mais complexas.

## AGRADECIMENTOS

Gostaria de agradecer a todas as partes envolvidas que contribuíram para este projeto, especialmente minha família e minha namorada. O presente trabalho foi realizado com apoio do CNPq, Conselho Nacional de Desenvolvimento Científico e Tecnológico – Brasil, por meio do programa PIBITI/CNPq-UFCG.

Também expresso minha gratidão à equipe do Laboratório de Eletrônica Industrial e Acionamento de Máquinas (LEIAM) da UFCG por fornecer o ambiente de pesquisa e os recursos necessários para a execução das atividades experimentais.

Agradeço a todos os colaboradores, colegas e professores, que contribuíram de maneira favorável ao projeto. Destaco meu professor orientador, Maurício Beltrão, e meu colega, Roberto Dourado, que foram fundamentais em todas as etapas deste trabalho.

## REFERÊNCIAS

- BIAVA, Hiuri; SALAMONI, Mariana; COELHO, Michella. **Implementação de um inversor multinível monofásico com seis chaves semicondutoras controlado por dispositivo FPGA.** TCC (Graduação) - Curso de Engenharia Elétrica - Universidade Tecnológica Federal do Paraná, Curitiba, 2016.

- SANTANA, Michel. **Uma Metodologia de Desenvolvimento do Controle Digital de Conversores Estáticos utilizando FPGA.** Tese (Mestrado em Engenharia Elétrica) - Universidade Federal de Itajubá, Itajubá, 2006.

- GRIGOLETTO, Felipe Bovolini. **Contribuição ao estudo de estratégias de modulação aplicadas a conversores multiníveis com diodos de grampeamento.** Tese (Mestrado em Engenharia Elétrica) - Universidade Federal de Santa Maria, Santa Maria, 2009.

- PIMENTEL, Sérgio. **Aplicação de Inversor Multinível como Filtro Ativo de Potência.** Tese (Mestrado em Engenharia Elétrica) - Universidade Estadual de Campinas, Campinas, 2006.

- CASTRO, Luis Gustavo. **Modulação Rápida para Inversores Multiníveis sem Transformação de Coordenadas.** Tese (Mestrado em Engenharia Elétrica) - Universidade Federal de Campina Grande, Campina Grande, 2013.

- BIN WU. **High-Power Converters and AC Drives.** 1st ed. New York: Wiley-IEEE Press, 2006.

ARAÚJO, Rômulo Diniz. **Projeto e Simulação de Filtros L e LCL para Interconexão de Inversor NPC Trifásico à Rede.** Tese (Mestrado em Engenharia Elétrica) - Universidade Federal do Ceará, Fortaleza, 2012.

MESQUITA, Samuel Jó de. **Uma Proposta de Projeto para Inversor Multinível em Cascata Assimétrico com 63 Níveis na Tensão de Saída e Operação em Baixa Frequência.** Tese (Mestrado em Engenharia Elétrica) - Universidade Federal do Ceará, Fortaleza, 2011.

Kathar, M. E., & Kulkarni, S. M. **Comparative Study of Multilevel Inverter Topologies.** PG Student, PES College of Engineering, Aurangabad (MS) India, 2017.

LACERDA FILHO, Antonio Venancio de Moura. **Novo inversor híbrido de cinco níveis alimentado por conversor cc-cc do tipo boost/flyback.** Tese (Mestrado em Engenharia Elétrica) - Universidade Federal da Paraíba, 2019.

COELHO, Carolina Antunes; FERNANDES, Leonardo Göbel. **Estudo e implementação de um inversor multinível monofásico controlado por FPGA para aplicações de ensino e pesquisa.** Trabalho de Conclusão de Curso. Universidade Tecnológica Federal do Paraná, Departamento Acadêmico de Eletrotécnica (DAELT), 2016.

IEEE Std 519-1992. **IEEE Recommended Practices and Requirements for Harmonic Control in Electrical Power Systems.** New York, NY: IEEE

MENDES, Laís Leal. **Simulação de conversores CC-CC em tempo real com FPGA.** Relatório de estágio supervisionado (Engenharia Elétrica) - Universidade Federal de Campina Grande, Campina Grande, 2015.

CAVALCANTI, Danilo Barreto. **Simulador tempo real baseado em FPGA de conversores CC-CC modulado.** Trabalho de Conclusão - Curso Engenharia Elétrica - Universidade Federal de Campina Grande, 2016.

BARROS, Samuel de Melo. **Análise por Simulação de Perdas em Conversor Estático PWM Utilizando Módulo FPGA.** Trabalho de Conclusão - Curso Engenharia Elétrica - Universidade Federal de Campina Grande, 2019.